| To Home |

|||

| 『DAS-703ES・アナログ回路部の解説』 (DAS-703ESのサービスマニュアルより抜粋掲載) |

|||

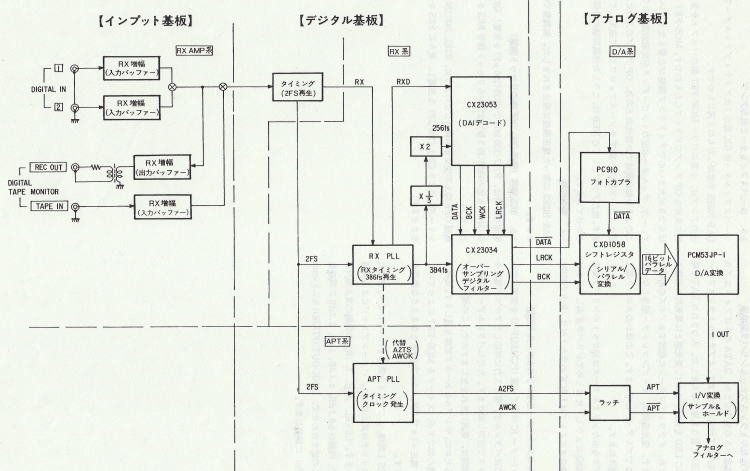

| ■システムブロックダイアグラム■ | |||

| 下記の図はDAS-703ESのシステムブロックダイアグラムを示した。システムブロックは、『インプット基板』、『デジタル基板』、『アナログ基板』の3つのブロックに大別される。 インプット基板とデジタル基板についての動作解説はここで説明されている。このページではアナログ基板について解説してみる。 |

|||

|

|

|||

|

|||

|

|

| 2 アナログ部 | |||

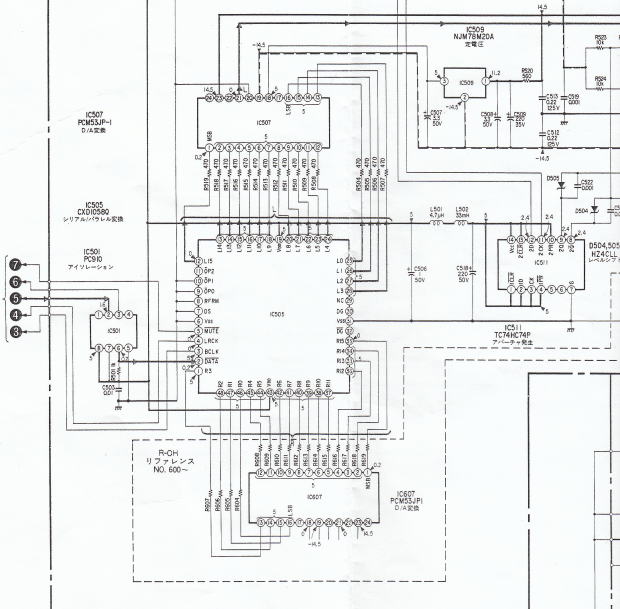

| 2−1 オプチカルトランスファーとシリパラ変換 (シリパラ変換=シリアルデータとパラレルデータを相互に変換) |

|||

| デジタル基板からの信号のうち、DATAのみはフォトカプラー(PC-910)を介して伝送している。これを「オプチカルトランスファー」(光学的伝送)と命名されている。 入力されたDATA電流は、内部のLEDを点灯させる。受光部とは電気的に切り離されているため、グランドリターンに起因するノイズの影響が避けられる。受光部側は、オープンコレクター相当となっており、1kΩでプルアップしている。他のクロック類は有線で接続される。 フォトカプラーを出たシリアルデータは32ビットのシリパラ変換IC CXD1058QによりL、Rまとめてシリパラ変換される。変換のタイミングはLRCKの立ち上がり(R chの終端)である。 |

|||

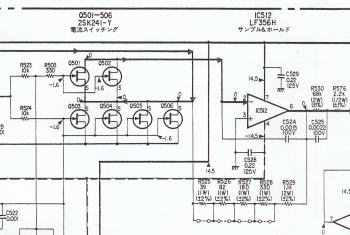

| 2−2 D/Aコンバーターとサンプル&ホールド回路 | |||

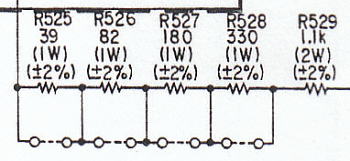

| D/AコンバーターICはラダー型(PCM53JP-1)を使用している。入力はパラレルで、常に入力に対応したアナログ電流をノンクロックで出力し続ける。ただし、パラレルデータが書き終わった瞬間は、電流に乱れを生じるため、この部分をデグリッチするために、サンプル&ホールド回路を通す。回路としてはポピュラーであるがスイッチにはMOS-FETを採用し、ゲート電圧+1VでON、−4VでOFFとなるような動作をさせている。 DAS-702ESと同様、ここでゲイン調整を行っている。音質上DAS-702ESで使用されていたディップスイッチは廃止し、パターンブリッジにいるゲイン調整方式としている。 「LEVEL ADJ. L(R)」のシルク印刷がある部分が調整箇所で、内側から0.2dB、0.4dB、1dB、2.2dBの調整量を持ち、この組み合わせで、LINE OUT(FIXED)を2.5Vrms(+10.2dBs)に調整する。 |

|||

■ LEVEL ADJ ■.  |

|||

|

|

|||

| ■D/Aコンバーター周辺回路■ |

|||

|

|||

| IC 507:PCM53JP-1・・・D/A変換 IC 505:CXD1058Q・・シリパラ変換 IC501:PC910・・アイソレーション(フォトカプラー) |

|||

|

|

|||

| ■サンプル&ホールド回路■ | |||

|

Q501〜Q506:2SK241・・電流スイッチング IC512:LF356H・・サンプル&ホールド |

||

|

|

|||

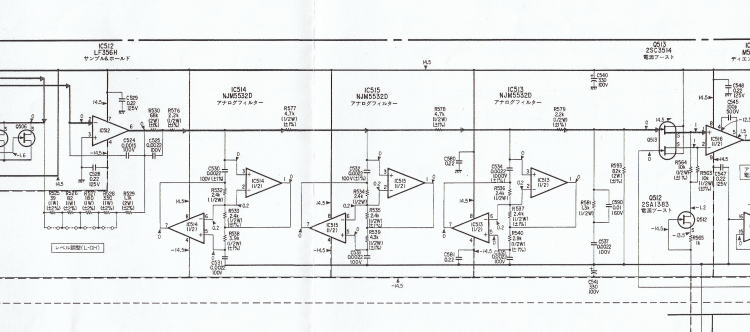

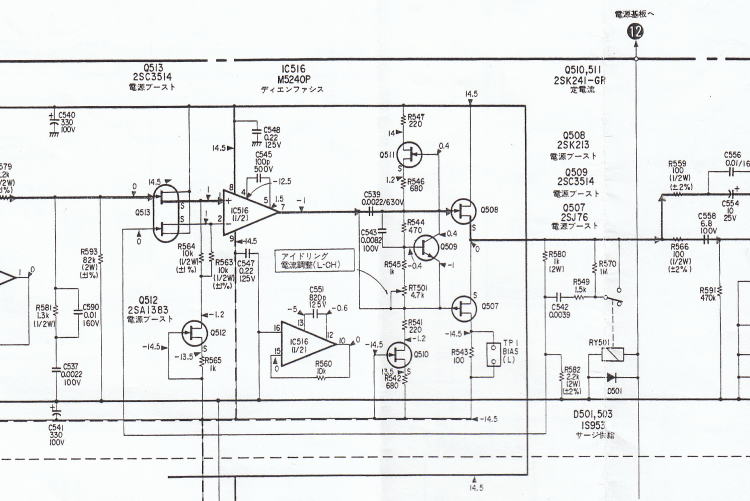

| 2−3 ローパスフィルターと出力アンプ | |||

| ローパスフィルターはGIC型7次アクティブフィルターで、DAS-702ESで採用されたものと同じ回路である。 出力アンプは、小型のパワーMOS-FETのバッファーを音質的に良好なOPアンプでドライブしている。MOS-FETのバラツキが大きいのでアイドリング調整が必要である。一方、フィルターの出力インピーダンスが高いので、このような動作環境での特性向上のため、OPアンプの入力に内部カスコード型のJ-FETをソースフォロワとして追加している。出力アンプとしてのNFBは、これら付属回路の外側からかけられている。 |

|||

|

|

|||

| ■ローパスフィルターの回路■ | |||

|

|||

|

|

|||

| ■出力アンプ(バッファーアンプ)部の回路■ |

|||

|

|||

|

|

|||

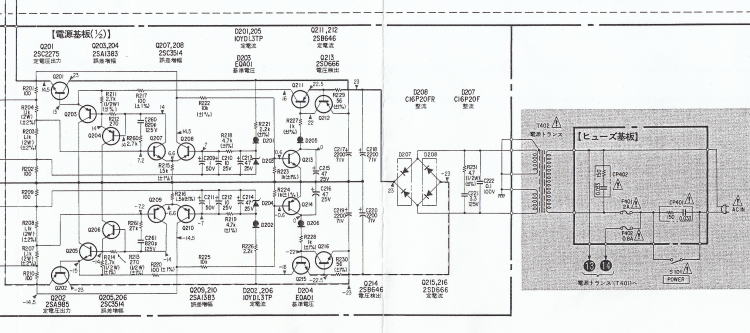

| 2−4 電源回路 |

|||

| 定電圧電源回路はアナログ系とデジタル系の2系統に分けられている。下記に示す回路図はアナログ系を示す。定電圧出力電圧は±14.5V、アナログ系回路に供給される。 DAS-702ESにあった電圧調整は廃止され、DAS-703ESは無調整回路としている。 |

|||

|

|

|||

| ■定電圧電源部の回路図■ | |||

|

|||

|

|

|||

| 2−5 RES回路(電源ON、OFF時のリセット回路) | |||

| 電源ON時は、R237(100kΩ)でC239(100μF)を充電し、Q219がONするまでの時間(約3秒)Q217からリセット信号RESを出力する。 電源OF時も不快なクリック音が発生しないように、R242、243(150Ωシリーズ)によりC241(100μF)を放電し、直ちにRESを発生させる。 |

|||

|

|

|||

| Copyright(c) 2008-2015 Masataka Ohnishi All Right Reserved |